GeneSys

GeneSys is an innovative solution designed to seamlessly integrate accelerators into the software infrastructure, offering a holistic approach to system design. It is specifically engineered to produce complete acceleration systems for emerging deep learning models with minimal human intervention. GeneSys marks a significant advancement in the realm of open-source deep learning hardware, presenting an all-in-one solution for the efficient generation of deep learning accelerators, complete with a cutting-edge compiler and user-friendly APIs. Next, we briefly list the key features of GeneSys.

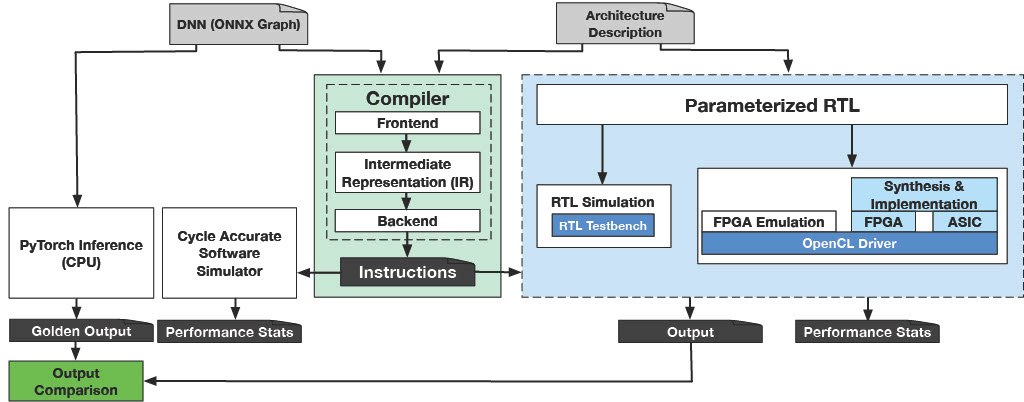

Comprehensive Solution: GeneSys offers an end-to-end compilation stack, a parameterizable DNN accelerator generator, RTL verification testbenches and regression suite with synthetic and state-of-the-art DNN benchmarks (including transformers like BERT and GPT2), FPGA implementation framework, OpenCL-compliant Linux drivers, and a software simulator for quick profiling and insights.

Multi-target Compilation Stack: The Codelet compiler converts ONNX models into an intermediate representation (IR) and performs architecture specific optimizations for various configurations. It further supports multiple backends, giving users flexibility in deploying tailored accelerators.

Accelerator Architecture: The GeneSys accelerator features a systolic array for operations such as GeMM and convolution, along with a closely coupled specialized SIMD unit for operations such as softmax, pooling, and activation. It is highly parameterizable and synthesizable.

Holistic Evaluation: GeneSys offers a holistic approach to evaluation, verification, and debugging for efficient design space exploration, encompassing hardware and compiler optimizations.

ONNX Compatibility: GeneSys utilizes the Open Neural Network Exchange (ONNX) format to specify deep learning models, ensuring interoperability across various programming environments. It can compile Pytorch/Tensorflow-generated models into the accelerator.

Minimal Python APIs: GeneSys provides minimal Python APIs for seamless integration into end-to-end applications, streamlining the development process.

AWS F1 FPGA Compatibility: GeneSys is compatible with AWS F1 instances available in the public cloud, enabling users to run end-to-end deep neural networks on these FPGA instances, enhancing its versatility and accessibility.

news

| Jun 29, 2024 | We presented our tutorial at the 51st Annual International Symposium on Computer Architecture (ISCA 2024) in Buenos Aires, Argentina. Check out the slides and corresponding videos here. |

|---|---|

| Apr 28, 2024 | We presented our tutorial at the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2024) in San Diego, CA, USA. Check out the slides and corresponding videos here. |

| Mar 2, 2024 | We presented our tutorial at the 30th IEEE International Symposium on High-Performance Computer Architecture (HPCA 2024) in Edinburgh, Scotland. Check out the slides and corresponding videos here. |

| Feb 16, 2024 | Our tutorial was accepted for presentation at the 51st Annual International Symposium on Computer Architecture (ISCA 2024) in Buenos Aires, Argentina. |

| Jan 17, 2024 | Our tutorial was accepted for presentation at the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2024) in San Diego, CA, USA. |